Heterogeneous Accelerated Compute Cluster

Under the scope of the external page AMD Xilinx University Program, the external page Heterogeneous Accelerated Compute Clusters (HACCs) is a special initiative to support novel research in adaptive compute acceleration for high-performance computing (HPC). The scope of the program is broad and encompasses systems, architecture, tools, and applications. HACCs are equipped with the latest AMD Xilinx hardware and software technologies for adaptive compute acceleration research. Each cluster is specially configured to enable some of the world’s foremost academic teams to conduct state-of-the-art HPC research.

Our group hosts one of the five HACCs sites worldwide (the others are two in the US, one in Germany, and one in Singapore).

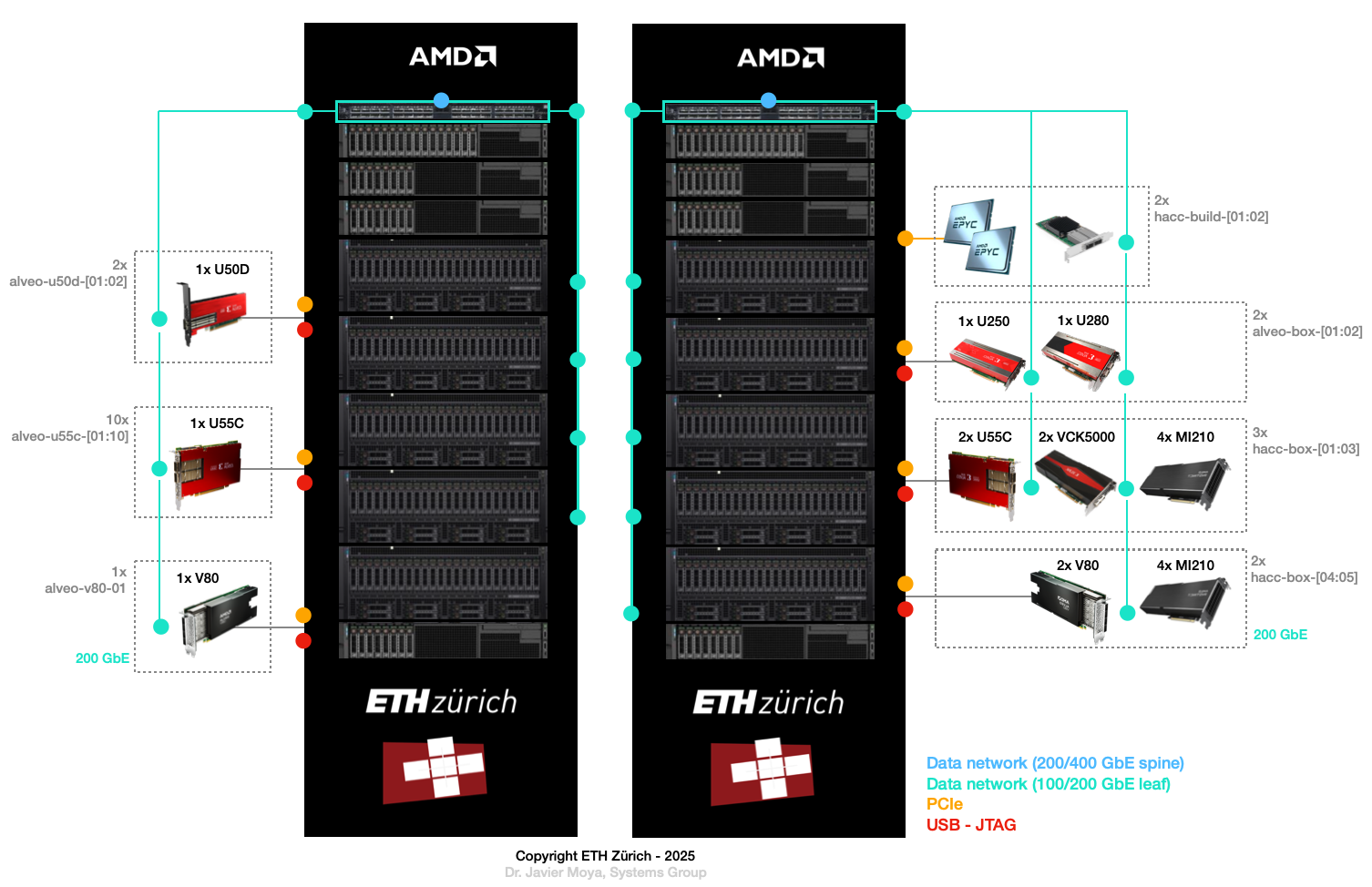

Infrastructure

ETHZ-HACC comprises high-end servers, Xilinx accelerator cards, and high-speed networking. Each accelerator card has all of its Ethernet interfaces connected to a 100 GbE leaf switch to allow exploration of arbitrary network topologies for distributed computing. Additionally, we are offering a build server with development and bitstream compilation purposes. For more information, please visit the external page Infrastructure section on GitHub.

AMD Xilinx hardware and software technologies

ETHZ-HACC offers the following external page adaptable accelerator cards:

- external page Alveo U250

- external page Alveo U280

- external page Alveo U50D

- external page Alveo U55C

- external page Alveo V80

- external page Versal VCK5000

We use Ansible Automation Platform for managing Xilinx’s tools versioning according to external page XRT’s release schedule. All servers equipped with an FPGA are associated with a unique software version, including XRT’s Xilinx Board Utility (xbutil), Xilinx tools (Vivado, Vitis_HLS, Vitis), and the flashable partitions (or base shell) running on the FPGA. For more information, please visit the external page Releases section on GitHub.

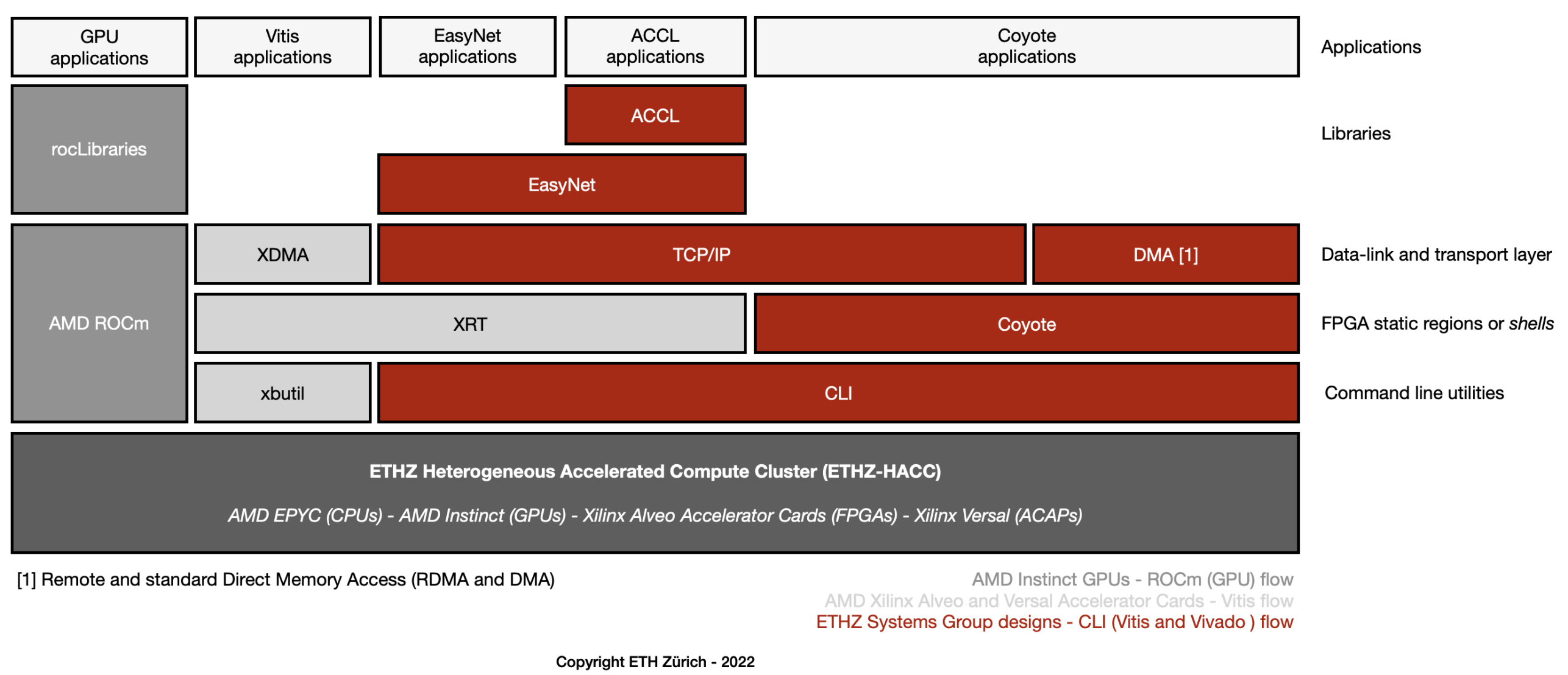

Hardware acceleration platform

As a multi-core, GPU, and FPGA cluster, ETHZ-HACC allows research in distributed systems, databases, cloud computing, and hardware acceleration of data science. Internally, we are using our ETHZ-HACC to conduct extensive research to assemble an Infrastructure for heterogeneous architectures and hardware acceleration. All our designs are open-source and available through our command-line interpreter external page CLI. With this initiative, we hope that ETHZ-HACC users will be able to develop their accelerated applications more quickly.

Get started

Researchers from academy and industry are invited to apply to the HACC program external page here. For researchers at ETH Zurich, please contact Prof. Dr. Gustavo Alonso. Once your account has been approved, you will receive a confirmation email with further details.

Tutorials

As part of our partnership program with AMD, we offer a series of tutorials teaching how to use our Hardware Acceleration Platform on the HACC:

- FPGA 2023: Enabling Networking for Distributed Applications on FPGA Clusters

- SIGMOD 2023: Data Processing on FPGAs with Modern Architectures

- FPL 2023: Network and Memory Abstractions on FPGAs for Distributed Applications

- ASPLOS 2025 Tutorial: Open-source infrastructure for FPGAs in the datacenter: from the OS to the network

- SOSP 2025 Tutorial: Open-source SmartNIC abstractions and infrastructure for AI and data analytics

People

external page Ruiz, Mario, Dr.

For more information about the people involved in this project, please visit the external page Who does what section on GitHub.